Smillsey

Member level 5

Hi all

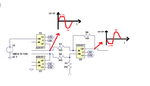

I have designed an IN AMP using LT Spice and the ADA4817 opamp model, but I am not getting results as expected. See the circuit and results below.

My question is: Why can't the signal swing to to negative rail?

Here is the datasheet for your reference :

https://www.analog.com/media/en/technical-documentation/data-sheets/ada4817-1_4817-2.pdf

The differential input range is meant to be +/-Vs isn't it? I would expect to be able to swing between +/-5V.

Is it a quirk of LTSpice?

However,on page 19 this statement confuses me : "The innovative high speed FET input stage handles common-mode signals from the negative supply to within 2.7 V of the positive rail."

Any help would be appreciated.

I am trying to design a +/-5V differential input with extremely high input impedance.

Thanks

S

I have designed an IN AMP using LT Spice and the ADA4817 opamp model, but I am not getting results as expected. See the circuit and results below.

My question is: Why can't the signal swing to to negative rail?

Here is the datasheet for your reference :

https://www.analog.com/media/en/technical-documentation/data-sheets/ada4817-1_4817-2.pdf

The differential input range is meant to be +/-Vs isn't it? I would expect to be able to swing between +/-5V.

Is it a quirk of LTSpice?

However,on page 19 this statement confuses me : "The innovative high speed FET input stage handles common-mode signals from the negative supply to within 2.7 V of the positive rail."

Any help would be appreciated.

I am trying to design a +/-5V differential input with extremely high input impedance.

Thanks

S