fadia

Newbie level 2

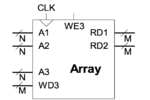

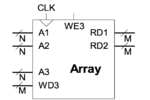

I want to test my register file before connecting it to ALU. So I wrote a testbench for my register file.

and this is my testbench

So with above conditions the testbench output rd1 and rd2 will be don't care, but when I set all the input to same number the output will work and will be same as input. I know this sound to me the output is following the input, but the schematic doesn't show that. So what could be reason for this situation.

Code Verilog - [expand]

and this is my testbench

Code Verilog - [expand]

So with above conditions the testbench output rd1 and rd2 will be don't care, but when I set all the input to same number the output will work and will be same as input. I know this sound to me the output is following the input, but the schematic doesn't show that. So what could be reason for this situation.

Last edited by a moderator: