Alpacca

Newbie level 6

Hello!

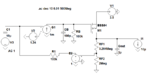

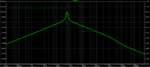

I was wondering - is it possible to obtain a phase margin over 180 degrees? Get positive phase at 0 dB gain? I'm designing LDO and I can't find the right value of output capacitor to get any phase margin.

Thanks in advance for explanation!

I was wondering - is it possible to obtain a phase margin over 180 degrees? Get positive phase at 0 dB gain? I'm designing LDO and I can't find the right value of output capacitor to get any phase margin.

Thanks in advance for explanation!