matt11

Newbie level 4

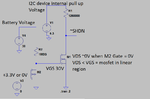

I have a current sense IC powered directly from a battery. I want the current sense IC to be in the shutdown state when the 3.3V power supply is disabled.

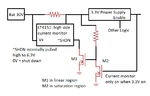

I have added a dual N channel MOSFET circuit (see attachments) to achieve a pull down on the shut down pin (active low and internally pulled high) when the

3.3V supply is not present. The circuit seems to work in LTspice but I am concerned about one of the MOSFETS operating in the linear region. (VDS < VGS - VT)

Is it safe to operate the MOSFET in this configuration or is there anything I'm missing that is considered bad design?

I have added a dual N channel MOSFET circuit (see attachments) to achieve a pull down on the shut down pin (active low and internally pulled high) when the

3.3V supply is not present. The circuit seems to work in LTspice but I am concerned about one of the MOSFETS operating in the linear region. (VDS < VGS - VT)

Is it safe to operate the MOSFET in this configuration or is there anything I'm missing that is considered bad design?