righteous

Full Member level 2

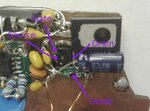

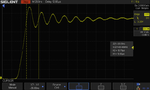

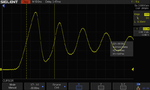

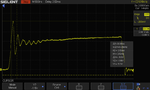

I'm still puzzled by what you are trying to achieve. It seems your circuit has no output and all you are doing is pulsing current through the coil then wondering why it shows a damped oscillation. The diode is connected directly across the coil and with the exception of it's turn-on time just clamps one polarity. Also note that the absolute maximum VDS of that MOSFET is 12V which you are exceeding. The layout is probably responsible for the 23MHz ringing, mounting the MOSFET on a small PCB and running wires to it is asking for trouble.

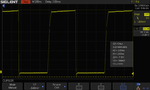

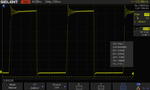

What drives the gate? We can't see the type when it is on it's edge. 820KHz is going to need quite a lot of gate drive power.

I also find it strange that a small air cored coil like that has 3 Ohms resistance - should be much less than that and almost certainly needs more inductance to be efficient.

Brian.

Brian,

Thank you for your comments. Allow me to try to explain as good as I can; I'm in this forum because I need your assistance, I'm lacking the valuable classical engineering training and the experience that comes along, therefore I would very much dislike to antagonize anyone here.

It seems your circuit has no output and all you are doing is pulsing current through the coil then wondering why it shows a damped oscillation.

You are right, I couldn't have expressed it more concisely myself. And I'm aware that makes me look like like I don't know what I want and why, but that is something I will have to live with because of two these two distinct reasons:

The first being embodied by the late Mr. Clarke, I'm paraphrasing here: "When a distinguished but elderly engineer states that something is possible, they are almost certainly right. When they state that something is impossible, they are very probably wrong."

The second reason being the Backfire Effect

So, - if you can fix the problem with the Backfire effect, I would be more than pleased to reduce any puzzlement that you may have.

maximum VDS of that MOSFET is 12V which you are exceeding.

Yes, I know, but it was never meant to exceed 6V, if that diode would just do as it is told ;-)

What drives the gate?

CMOS output into a B882/772 totempole, should be enough I believe.

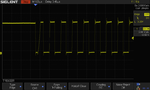

The layout is probably responsible for the 23MHz ringing

I will change the layout and let you know the results. I note that CataM is also suggesting the same.

I also find it strange that a small air cored coil like that has 3 Ohms resistance

That is what I measure across the terminals. 0,05mm wire has about 0.5 Ohm per Meter.

should be much less than that and almost certainly needs more inductance to be efficient.

Can you please elaborate what you mean by "efficient" ? I'm not sure I understand?

- - - Updated - - -

Move the inductor closer to the FET. You have big leads for the inductor, which likely are the reason for the 21.4 nH stray inductance. Inductor-FET-freewheeling diode --> All close together.

Thank you, out of sincere interest, can you please tell me how you deduct this causality?

- - - Updated - - -

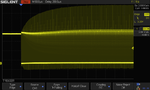

Besides the dubious circuit purpose, it's quite difficult to read the experiment results. I don't see a single waveform with a clear description which voltage or current has been actually probed.

Can you please guide on how I should conduct the measurements so that they are clear, I mean - what did I miss?

- - - Updated - - -

Hello righteous,

The ringing is indeed caused by parasitic components associated with the physical realisation of this circuit, namely L and C that are not shown in the circuit schematic, but which exist in reality due to various factors. May I make 4 points that may help reduce the ringing effects, with reference to the sketch below (the quality of which I aplogise for, but a pencil and paper is all that I had).

1. Minimise the stray inductance contained in the loop enclosed by these three components: (a) the capacitor (b) the MOSFET (c) the diode. This is done by keeping component lead lengths short and minimizing the **area** of the circuit.

2. To reduce the parasitic L of the capacitor, connect a number of capacitors (of smaller value) in parallel rather than use one capacitor of larger value.

3. The length and the layout of the wires that connect the inductor to the circuit is not that important. The coil is already an inductor, so adding more parasitic L via longer wires is not going to contribute to the ringing. Use this fact to help acheive goals 1 and 2 above. The same can be said for the connection to the power supply, however if that voltage source is connected via significant parastic L then ensure there is plenty of C to "hold-up" the voltage of the loop mentioned in 1.

4. The connection of the gate driver to the MOSFET gate is important. In particular, the connection to the source terminal must be done as close to the component as possible to minimise including any L that carries the load current within the gate circuit. The gate drive should be low impedance, so standard circuit layout techniques should be applied such as (a) gate drive circuit to have good power suppy de-coupling capacitors, (b) small loop area from the de-coupling caps to the gate driver to the MOSFET (use twisted wires if necessary).

Even after all these actions have been applied, there still may be ringing, in which case standard snubbers (clamping type, and ramp-limiting type) may need to be applied, depending on what your final application is.

Hope this helps.

I just tried to load the image, but I am not sure it worked. If it did not, then I will try to load the image in my next post.

View attachment 143744

cascoder,

Thank you for your input.

Ad 1. Thank you again, its very clear from the drawing what you mean, I see it now.

Ad 2. Check - will do.

Ad 3. That seems to contradict the consensus here? Though my personal logic would be in line with yours "The coil is already an inductor, so adding more parasitic L via longer wires is not going to contribute to the ringing."

Ad 4. it's connected pin-to-pin, there is a total of 6mm of exposed wire in this connection.

Actually I think I will try to measure the inductance and let you know, I will be using this method

Last edited: