Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

That looks right to me.

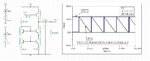

When the pulse is low, the transistor is not conducting so the capacitor quickly charges to 12V through R1.

During the pulse period, the transistor turns fully on and the voltage across the capacitor will drop due to the potential divider of R1 and R3 plus a residual C-E voltage in the transistor.

Pulse low = 12V

Pulse high = 11.921V + the transistor's CE voltage.

If you were expecting more of a sawtooth 'ramp' you have to disconnect the 12V during the discharge period.

Brian.

Let's all back up here a minute; OP what are you really trying to accomplish? The fundamental problem here is in the OPs statement "charging with lower resitance and discharging with higher resistance". What you are actually doing is charging with a lower resistance CONTINUOUSLY and discharging with a higher resistance for a teeny-tiny amount of time. Are you actually trying to generate a sawtooth? Just using RCs won't work, you'll get exponential edges. And you don't need two PNPs for a 'shoddy' constant-current source; you can make a very nice one with one PNP.

Hi,

Only later did I see the word comparator in your description, sorry about that... Maybe someone more experienced can think of a simpler solution; I tried a few things with an open drain comparator and the only design I got to work requires an additional NPN,so maybe it's no use to you. I had to use a 5V comparator in the simulation as I haven't found any others that I'm familiar with such as the 339, same difference, just a matter of voltage used.

I think, and I might be wrong, a problem with the original idea of yours may be that when the comparator is on (i.e. draining) then it is also going to drain the capacitor quickly, so the slowly discharging capacitor needs to be isolated from that with an additional component so as to drain in its own time and not pulled down by the comparator sinking anything in its path.

Not sure what you're connecting the comparator to, but with this latest circuit, I'd buffer it with a voltage follower, in the simulation it only raises the lowest voltage to ~50mV rather than a solid 0V without a buffer.

View attachment 143737