Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

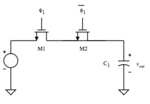

Should I use Transmission Gates for the Switches shown in the figure below ?

This depends on the potential (voltage levels) between the nodes you want to switch:1. Why not use all transmission gate switches ?

See here:2. What do you mean by NMOS switches with a second anti-phase switched NMOS Cap ? What is an anti-phase switched NMOS cap ? Sorry for my ignorance on this topic.

Find here an explanation.

Find here an explanation.Right!3. So when you say PMOS switches you just mean PMOS switches by themselves, obviously.

How about the switches internal to the diff amp, they are not tranmission gates right.

Just used NMOS tranmission gates or do I use PMOS ?

These switches are external to the diff amp! Node voltages to be switched are unknown - here you need transmission gates!I marked up my original attachment - so I am sure the ones I circled in blue can be NMOS switches, and somewhat sure the ones in red can also be NMOS switches.

https://www.edaboard.com/attachment.php?attachmentid=144026&d=1516237430

In order to reduce charge injection, you should add a second anti-phase switched MOS Cap in series with each proper switch, i.e. for transmission gates, too.Is this where I should add the NMOS switches with a second anti-phase switched NMOS Cap as you had previously suggested as well ?