ICdesignerbeginner

Member level 5

Hi

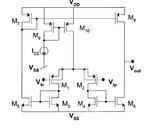

Can some one help me in understanding this OTA confguration. I have seen different OTA configuration but this OTA configuration attached below has three current mirrors to pass the current to the output. What about the ac current? I think current mirrors work for DC currents then how will ac current appear at output?

Can some one help me in understanding this OTA confguration. I have seen different OTA configuration but this OTA configuration attached below has three current mirrors to pass the current to the output. What about the ac current? I think current mirrors work for DC currents then how will ac current appear at output?