deveshkm

Member level 4

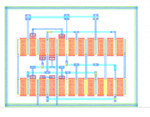

This is the schematic. i am doing the layout for this

Each transistor has 4 fingers each

The three transistors on the right are for dummy

pp pn np nn are gate inputs

A: pp B: pn

C: np D: nn

I am using the following scheme

ABBA (DUMMY) CDDC

DCCD (DUMMY) BAAB

The routing is quite complex.

The layout is not complete , yet

Please suggest better scheme or tips on layout for this.

Each transistor has 4 fingers each

The three transistors on the right are for dummy

pp pn np nn are gate inputs

A: pp B: pn

C: np D: nn

I am using the following scheme

ABBA (DUMMY) CDDC

DCCD (DUMMY) BAAB

The routing is quite complex.

The layout is not complete , yet

Please suggest better scheme or tips on layout for this.