blooz

Advanced Member level 2

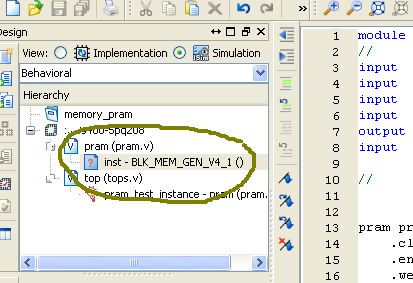

What is the basic difference between the .mif and .coe files ...When you generate a RAM block using the Xilinx Core genrator the .coe file is loaded ,but when simulating there appears a message saying that .mif not found .Is .coe file enough for implementing on FPGA and .mif for simulation .Could you please clarify the matter ?

here is the message

/////////////////////////

ISim M.53d (signature 0xb869381d)

This is a Full version of ISim.

Time resolution is 1 ps

Simulator is doing circuit initialization process.

Block Memory Generator CORE Generator module loading initial data...

WARNING: at 0 ps: file pram.mif could not be opened

////////////////////////////

here is the message

/////////////////////////

ISim M.53d (signature 0xb869381d)

This is a Full version of ISim.

Time resolution is 1 ps

Simulator is doing circuit initialization process.

Block Memory Generator CORE Generator module loading initial data...

WARNING: at 0 ps: file pram.mif could not be opened

////////////////////////////