thanhtri_pc

Junior Member level 2

hi all,

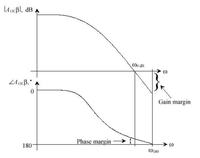

I want to determine the gain and pharse margin of the Op-amp (open-loop only). So I draw the schematic as attachment.

The input is Vsin signal and I run AC analysis (using Spectre simulaor). After simulating, I realize that with different magnitude of Vsin, I got different values of gain/pharse margin. I would like to ask how to choose the magnitude value of Vsin to get valid gain/pharse margin?

Many helps are welcome!

I want to determine the gain and pharse margin of the Op-amp (open-loop only). So I draw the schematic as attachment.

The input is Vsin signal and I run AC analysis (using Spectre simulaor). After simulating, I realize that with different magnitude of Vsin, I got different values of gain/pharse margin. I would like to ask how to choose the magnitude value of Vsin to get valid gain/pharse margin?

Many helps are welcome!