flote21

Advanced Member level 1

Hello dudes!

I am wondering if the next circuit will work a I expected.

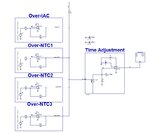

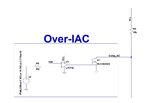

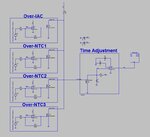

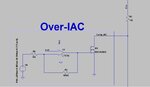

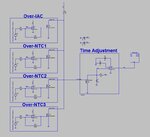

I want to design a signal conditioning stage with some opamps working like comparators. These opamps compare an incomming voltage with a reference voltage and they generate an "enable" signal to control a digital buffer. In the previous pic I have used NMOS trt's in order to generate an open drain output. I have simulated the behaviour of the circuit and it looks working as I expected. However i would like to ask someone in the forum if I could have any problem in the real life...Maybe I am skipping something.

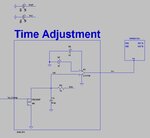

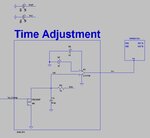

Further, once the buffer is disabled, it is also important to control the enable of the buffer. In order to do that I have thought to use combination of RC network and opamp. I have also simulated the circuit and it looks works fine but I would like to know the opinion of the people here, because maybe they have better ideas...

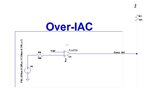

In the simulations every opamp had a one impuse spaced between them 100us.

And the time adjustment circuit looks works like I expect. If the pulses are fast, the err signal goes low instantaneously. but it recovers its natural state after the delay introduced by the RC network...

Thanks in advance.

I am wondering if the next circuit will work a I expected.

I want to design a signal conditioning stage with some opamps working like comparators. These opamps compare an incomming voltage with a reference voltage and they generate an "enable" signal to control a digital buffer. In the previous pic I have used NMOS trt's in order to generate an open drain output. I have simulated the behaviour of the circuit and it looks working as I expected. However i would like to ask someone in the forum if I could have any problem in the real life...Maybe I am skipping something.

Further, once the buffer is disabled, it is also important to control the enable of the buffer. In order to do that I have thought to use combination of RC network and opamp. I have also simulated the circuit and it looks works fine but I would like to know the opinion of the people here, because maybe they have better ideas...

In the simulations every opamp had a one impuse spaced between them 100us.

And the time adjustment circuit looks works like I expect. If the pulses are fast, the err signal goes low instantaneously. but it recovers its natural state after the delay introduced by the RC network...

Thanks in advance.