Junus2012

Advanced Member level 5

Hello,

I am simulating the slew rate of fully differential OTA. I have a problem with making buffer using resistive network, first I can't choose small value of R because this will kill the gain of the OTA, secondly if I use a big resistors it creates in conjunction with the input MOSFET a pole at low frequency that disturb the stability of my amplifier.

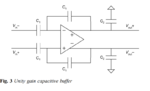

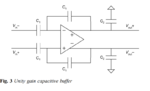

By looking in to this problem I have serched and found many authors are testing the lsew rate using pure capacitive network as shown in the figure below,

My question is what is the total effective or equivalent capacitive load seen at the differential output ?

My second question, can we simulate the slew rate from open loop ? I belive that we can but we will not get an information about phase margin and GBW

Thank you very much

I am simulating the slew rate of fully differential OTA. I have a problem with making buffer using resistive network, first I can't choose small value of R because this will kill the gain of the OTA, secondly if I use a big resistors it creates in conjunction with the input MOSFET a pole at low frequency that disturb the stability of my amplifier.

By looking in to this problem I have serched and found many authors are testing the lsew rate using pure capacitive network as shown in the figure below,

My question is what is the total effective or equivalent capacitive load seen at the differential output ?

My second question, can we simulate the slew rate from open loop ? I belive that we can but we will not get an information about phase margin and GBW

Thank you very much