Junus2012

Advanced Member level 5

Dear friends,

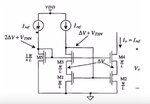

I attached you the picture of the wide swing current mirror and here is my question please,

As I understood from every literature I read that the transistor M5 (by referring to the circuit) has to be four times less than other transistors to get minimum output voltage equal to two saturation currents of M4 and M2 :

Vomin = VDS4 (sat)+VDS2 (sat).

This relationship (M5 = 1/4 M1 = 1/4 M2 = 1/4 M4 = 1/4 M2) is only true if the current in all the branches of this mirror is equal.

Now suppose if we want to mirror the current with different ration from the input, how we will select M5.

Suppose also if we use this mirror in the folded cascoded amplifier for the output cascoded stage where the current in the mirror is varying with the input, again how we will choose the right value of M5

Thank you very much in advance

I attached you the picture of the wide swing current mirror and here is my question please,

As I understood from every literature I read that the transistor M5 (by referring to the circuit) has to be four times less than other transistors to get minimum output voltage equal to two saturation currents of M4 and M2 :

Vomin = VDS4 (sat)+VDS2 (sat).

This relationship (M5 = 1/4 M1 = 1/4 M2 = 1/4 M4 = 1/4 M2) is only true if the current in all the branches of this mirror is equal.

Now suppose if we want to mirror the current with different ration from the input, how we will select M5.

Suppose also if we use this mirror in the folded cascoded amplifier for the output cascoded stage where the current in the mirror is varying with the input, again how we will choose the right value of M5

Thank you very much in advance