promach

Advanced Member level 4

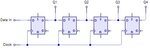

Why do RD_DATA and wDataShift need bitwidth of "[(C_DEPTH+1)*C_WIDTH-1:0]" in the following "shift register" module ?

Code Verilog - [expand]