hktk

Junior Member level 3

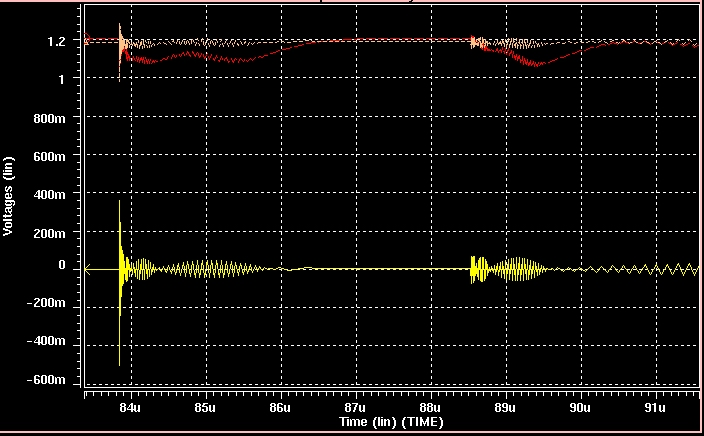

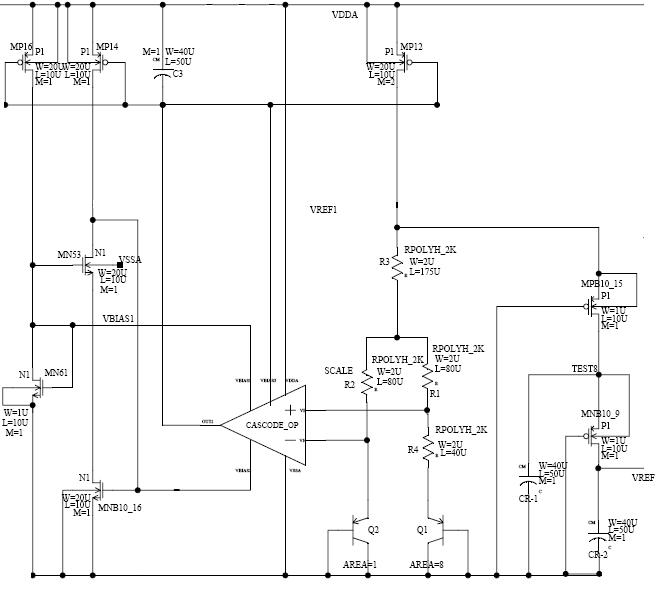

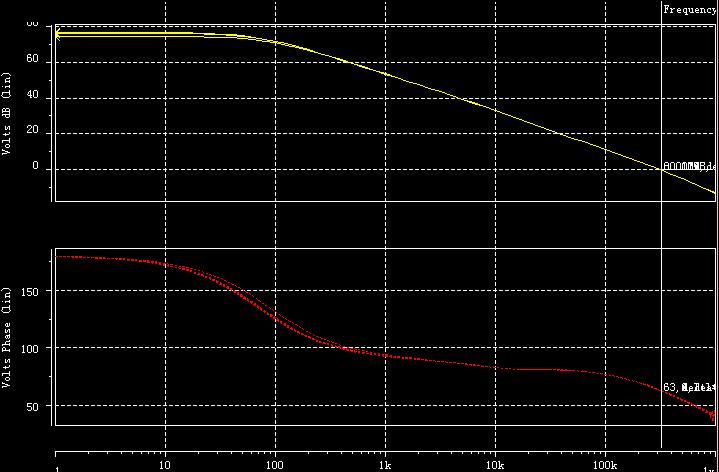

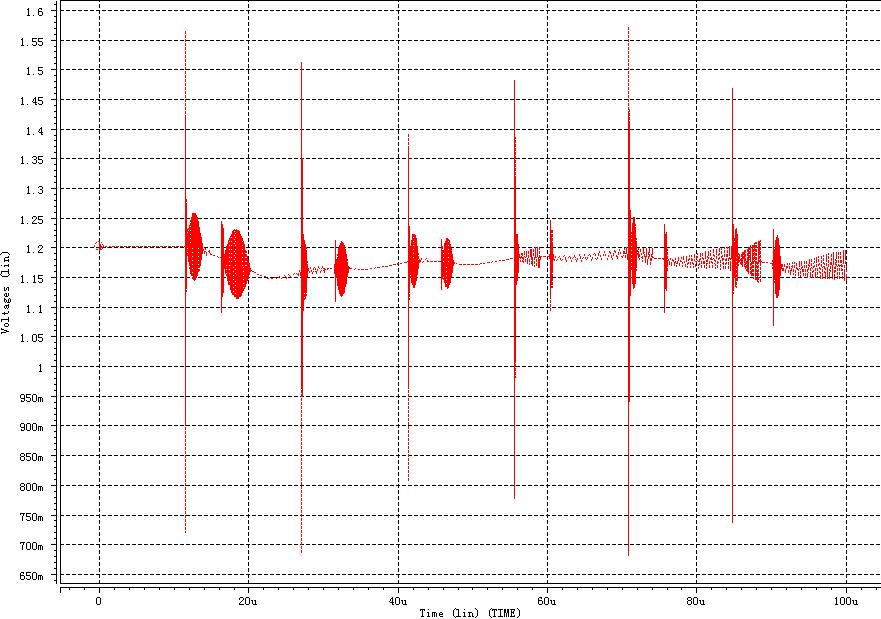

Hello, everyone. I meet a reference simulation problem and the following figure is the schematic and simulation results. When I put the reference circuit in the whole chip simulation with bonding model, the output of the reference has a large ripple with the switch frequency. When I just simulate the reference block, the loop characteristics are good enough. Can u guys give some advice about this? Hope for ur reply.

Schematic of Reference without start-up circuit

loop gain and phase simulation results

Simulation Results in whole chip with bonding model

Schematic of Reference without start-up circuit

loop gain and phase simulation results

Simulation Results in whole chip with bonding model