zhangseong

Member level 2

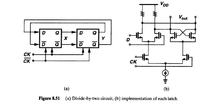

my design is to replace PLL to get a 50% duty cycle....my design include a gilbert cell as a frequency multiplier follow by a frequency divider(divide by 2 -D flip-flop)

jitter problem for input is ignored...my input is just a pulse wave(~48Mhz) so phase lock i ignore

my question is .. is this simple design will be succcesfull?

is this combination of gilbert cell and D-flip flop will get 50% duty cycle output?

##i can get frequency doubled using gilbert cell

##i can get a 50% divided output after D flip flop

##i have not combine the 2 things

jitter problem for input is ignored...my input is just a pulse wave(~48Mhz) so phase lock i ignore

my question is .. is this simple design will be succcesfull?

is this combination of gilbert cell and D-flip flop will get 50% duty cycle output?

##i can get frequency doubled using gilbert cell

##i can get a 50% divided output after D flip flop

##i have not combine the 2 things