sixdegrees

Junior Member level 2

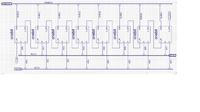

error posedge , 800ps

Hello,

I am using a Spartan 3 FPGA board and am having problems in the Post Place n Route simulation using Xilinx ISE 7.1i and ModelSim XE 6.0a.I have unnecessary glitches which causes garbage outputs before the output finally settles. Not only in large designs(I am designing IP core for a DSP proc.) if i instantiate a simple register,the post PnR simulation results shows glitches.

Below is the code and testbench for a simple 8bit register.

`timescale 1ns / 1ps

module top(in, clk, reset, enb, out);

input [7:0] in;

input clk;

input reset, enb;

output [7:0] out;

reg [7:0] out;

always @(posedge clk)

begin

if(reset)

out <= 8'b0;

else if(enb)

out <= in;

else

out <= out;

end

endmodule

module test_top_v;

// Inputs

reg [7:0] in;

reg clk;

reg reset, enb;

// Outputs

wire [7:0] out;

// Instantiate the Unit Under Test (UUT)

top uut (

.in(in),

.clk(clk),

.reset(reset),

.enb(enb),

.out(out)

);

always #25 clk = ~clk;

initial begin

// Initialize Inputs

in = 0;

clk = 0;

enb = 0;

reset = 1;

// Wait 100 ns for global reset to finish

#100;

#50 reset=0;

// Add stimulus here

#50 enb = 1;

in = 8'b00000001;

#50 enb = 0;

#180 enb = 1;

in = 8'b11111111;

#50 enb = 0;

#100 $stop;

end

endmodule

I get output glitches when the 'in' values changes from 8'h1 to 8'hFF.

Can someone plz give me some advice on how to get around all these problems and any links/pointers to get a robust and perfect design. I seem to get the idea that FPGA coding for implementation is quite a different ballgame as regards to functional simulation

Kool

Hello,

I am using a Spartan 3 FPGA board and am having problems in the Post Place n Route simulation using Xilinx ISE 7.1i and ModelSim XE 6.0a.I have unnecessary glitches which causes garbage outputs before the output finally settles. Not only in large designs(I am designing IP core for a DSP proc.) if i instantiate a simple register,the post PnR simulation results shows glitches.

Below is the code and testbench for a simple 8bit register.

`timescale 1ns / 1ps

module top(in, clk, reset, enb, out);

input [7:0] in;

input clk;

input reset, enb;

output [7:0] out;

reg [7:0] out;

always @(posedge clk)

begin

if(reset)

out <= 8'b0;

else if(enb)

out <= in;

else

out <= out;

end

endmodule

module test_top_v;

// Inputs

reg [7:0] in;

reg clk;

reg reset, enb;

// Outputs

wire [7:0] out;

// Instantiate the Unit Under Test (UUT)

top uut (

.in(in),

.clk(clk),

.reset(reset),

.enb(enb),

.out(out)

);

always #25 clk = ~clk;

initial begin

// Initialize Inputs

in = 0;

clk = 0;

enb = 0;

reset = 1;

// Wait 100 ns for global reset to finish

#100;

#50 reset=0;

// Add stimulus here

#50 enb = 1;

in = 8'b00000001;

#50 enb = 0;

#180 enb = 1;

in = 8'b11111111;

#50 enb = 0;

#100 $stop;

end

endmodule

I get output glitches when the 'in' values changes from 8'h1 to 8'hFF.

Can someone plz give me some advice on how to get around all these problems and any links/pointers to get a robust and perfect design. I seem to get the idea that FPGA coding for implementation is quite a different ballgame as regards to functional simulation

Kool