holddreams

Full Member level 6

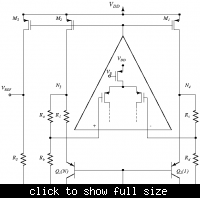

The attachment is the circuit of razavi's book ,figure 11.9.

My questions are:

1.How can I simulate the stability of this bandgap circuit?

2.Can we exchange the OPAMP input ?That is ,let the negative input connect with the A ,and the positive input connect with nA?

Thanks.

My questions are:

1.How can I simulate the stability of this bandgap circuit?

2.Can we exchange the OPAMP input ?That is ,let the negative input connect with the A ,and the positive input connect with nA?

Thanks.