yefj

Advanced Member level 4

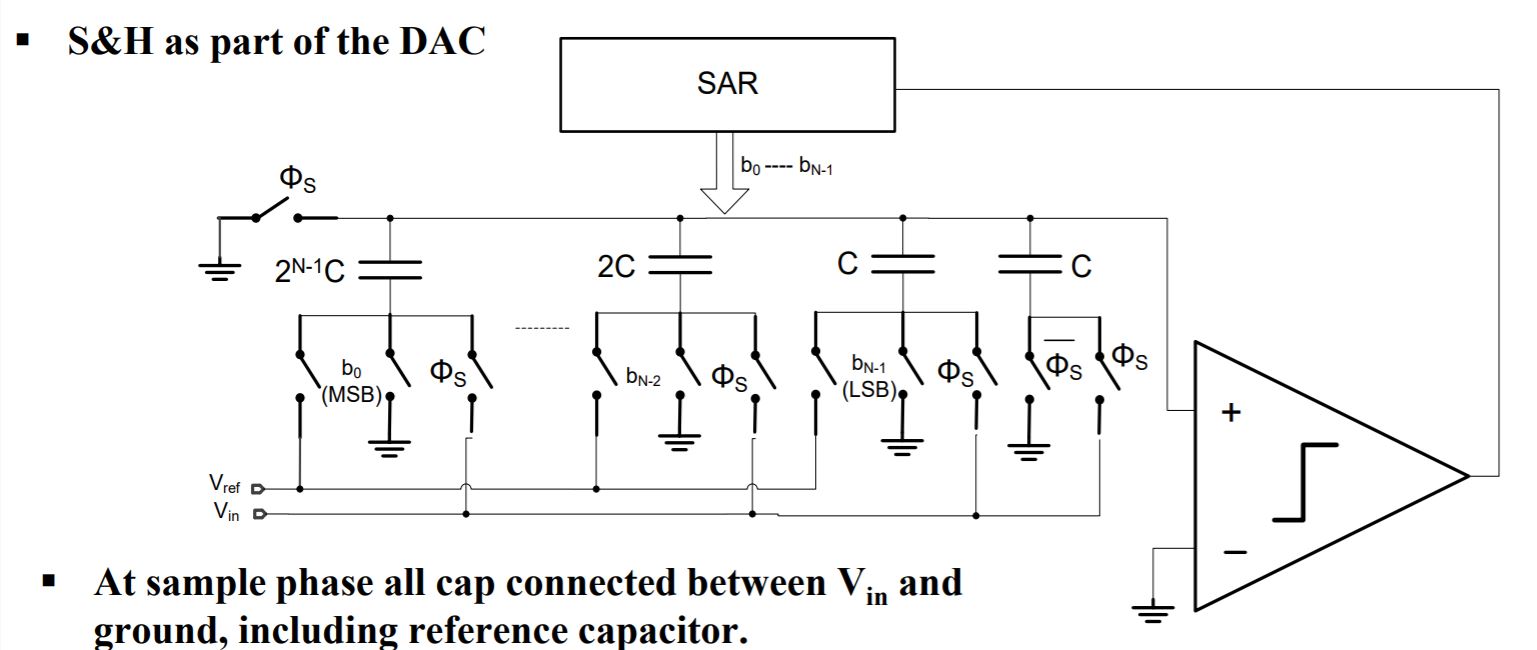

Hello , In the SAR ADC converter shown bellow, there is a basic logical problem.

Because we are comparing DC voltage to DC voltage in the proccess shown Bellow.

Thae comperator (which is implemented as OPAMP) has GND connected to it.All the calculations we assume a virtual ground.

But there is a contadiction because if we compare DC voltages then we have BIAS voltages on the input of the OPAMP.

a virtual ground exists if we have AC signal which is not the case in SAR ADC.

Where did i go wrong?

Thanks.

Because we are comparing DC voltage to DC voltage in the proccess shown Bellow.

Thae comperator (which is implemented as OPAMP) has GND connected to it.All the calculations we assume a virtual ground.

But there is a contadiction because if we compare DC voltages then we have BIAS voltages on the input of the OPAMP.

a virtual ground exists if we have AC signal which is not the case in SAR ADC.

Where did i go wrong?

Thanks.

Last edited by a moderator: