ranaya

Advanced Member level 4

Hi All,

I am doing a P&R experiment for a shift register which looks like below :

**broken link removed**

As you can see, it's composed of MUXs and Flip-Flops. Basically the input MUX of every Flip-Flop chain feeds the data to the chain and the data can also be interchanged between two parallel chains using the same MUXs. For now I only do this experiment for the typical corner at 0.6V (TT, 25C). From the (pre-layout) synthesis, it was confirmed that the system can operate at 240 MHz with sufficient setup/hold margins. P&R is intended for 200MHz and the related settings/constraints look like below :

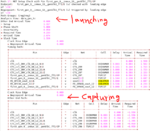

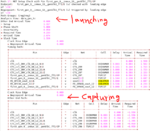

So in the routed design I do not see any violations and DRC related issues. There were no setup and hold issues either in the design. The intended CCOPT constraints have also been met. But I strangely find some buffers (CKBUF*) inserted between the Q-D pins of consequent flops in the design even with a sufficient slack time left between them. i.e. See following timing report :

So we have enough slack time in this path. The input cap load of both CKBUFM2R and the D input of the capturing flop are similar, and I don't see any reason to use this buffer in between. As you can see, even with the uncertainty of the clock, the difference of the clock signal arrival between the launching and capturing flops is quite small and with the large CP-Q delay of the launching flop, there should not be any hold violation without the buffer CKBUFM2R (If yes, Innovus would have used Delay elements in the list). So basically I do not see any reason to have these buffers in between. Even at a lower frequency, I see the same buffer count between the flops in the design. What could possibly be the reason for this ?

Thanks

Anuradha

I am doing a P&R experiment for a shift register which looks like below :

**broken link removed**

As you can see, it's composed of MUXs and Flip-Flops. Basically the input MUX of every Flip-Flop chain feeds the data to the chain and the data can also be interchanged between two parallel chains using the same MUXs. For now I only do this experiment for the typical corner at 0.6V (TT, 25C). From the (pre-layout) synthesis, it was confirmed that the system can operate at 240 MHz with sufficient setup/hold margins. P&R is intended for 200MHz and the related settings/constraints look like below :

Code:

SDC :

set_units -time ns -resistance kOhm -capacitance pF -voltage V -current mA

create_clock [get_ports clk] -period 5 -waveform {0 2.5}

set_clock_uncertainty 0.05 [get_clocks clk]

set_input_delay -clock clk -max 0.3 -all_inputs

set_output_delay -clock clk -max 0.3 -all_outputs

set_load -pin_load 0.004 -all_outputs

Critical Innovus Settings :

setAnalysisMode -analysisType single -checkType setup -skew true -clockPropagation sdccontrol

set_ccopt_property buffer_cells { CKBUFM8R CKBUFM6R CKBUFM4R CKBUFM3R CKBUFM2R CKBUFM1R }

set_ccopt_property inverter_cells { CKINVM8R CKINVM6R CKINVM4R CKINVM3R CKINVM2R CKINVM1R }

set_ccopt_property delay_cells { DEL1M1R DEL1M4R DEL2M1R DEL2M4R DEL3M1R DEL3M4R DEL4M1R DEL4M4R }

# Include this setting to use inverters in preference to buffers

set_ccopt_property use_inverters true

set_ccopt_property target_max_trans 600ps

set_ccopt_property target_skew 600ps

create_ccopt_clock_tree_spec

ccopt_designSo in the routed design I do not see any violations and DRC related issues. There were no setup and hold issues either in the design. The intended CCOPT constraints have also been met. But I strangely find some buffers (CKBUF*) inserted between the Q-D pins of consequent flops in the design even with a sufficient slack time left between them. i.e. See following timing report :

So we have enough slack time in this path. The input cap load of both CKBUFM2R and the D input of the capturing flop are similar, and I don't see any reason to use this buffer in between. As you can see, even with the uncertainty of the clock, the difference of the clock signal arrival between the launching and capturing flops is quite small and with the large CP-Q delay of the launching flop, there should not be any hold violation without the buffer CKBUFM2R (If yes, Innovus would have used Delay elements in the list). So basically I do not see any reason to have these buffers in between. Even at a lower frequency, I see the same buffer count between the flops in the design. What could possibly be the reason for this ?

Thanks

Anuradha

Last edited: