ajaz

Newbie level 2

Hi All,

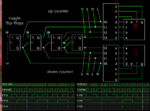

can anyone share me basics of clk and rst - i can't able to visualize when to use posedege and negedge.

Please suggest me Material or video. it would be great help for me.

can anyone share me basics of clk and rst - i can't able to visualize when to use posedege and negedge.

Please suggest me Material or video. it would be great help for me.