d123

Advanced Member level 5

Hi,

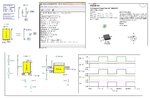

Circuit purpose is to sense presence of a resistive load in order to enable an SMPS and LDO (the 5V input) before a mechanical switch is turned on, otherwise SMPS and LDO should be off to save Iq.

It worked correctly with only Q1 + Q2 and the difference amplifier and comparator. With Q3 +Q4 (and then adding Q5 + Q6 to isolate X node from difference amplifier when 5Vout is enabled), this circuit simulates terribly: either 5V output overrides 2.662V output or it oscillates on and off when delay RCs are used on 5Vout drive circuit, and similar failed workarounds. Adding pull-downs to common-drain connections or difference amplifier Y point/node doesn't help.

I'n guessing it may be related to lack of understanding of interplay of source and drain voltages and some naïve design error at node X?

Can an adult tell me what must be obvious that I just don't grasp, please?

Circuit purpose is to sense presence of a resistive load in order to enable an SMPS and LDO (the 5V input) before a mechanical switch is turned on, otherwise SMPS and LDO should be off to save Iq.

It worked correctly with only Q1 + Q2 and the difference amplifier and comparator. With Q3 +Q4 (and then adding Q5 + Q6 to isolate X node from difference amplifier when 5Vout is enabled), this circuit simulates terribly: either 5V output overrides 2.662V output or it oscillates on and off when delay RCs are used on 5Vout drive circuit, and similar failed workarounds. Adding pull-downs to common-drain connections or difference amplifier Y point/node doesn't help.

I'n guessing it may be related to lack of understanding of interplay of source and drain voltages and some naïve design error at node X?

Can an adult tell me what must be obvious that I just don't grasp, please?

Last edited: