DavidYebadlo

Junior Member level 1

Hi,

I need to calculate and draw asymptotes on the oscilloscope.

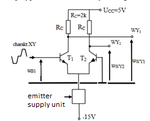

The tested system looks as follows:

One change - Rc = 20k Ohms.

I know that for voltage Ub1 in range for +-0.1V (approximately) transistor T2 is in the active mode. And i notice that Uwy1 is constant and this voltage is 5V. So transistor T1 is in cut-off mode. But i don't know how T2 transistor works when Ub1 voltage is less than -0.1V and when Ub1 voltage is greater than 0.1V. Does it work in saturation mode? Could you explain me?

Thanks for the help in advance!

I need to calculate and draw asymptotes on the oscilloscope.

The tested system looks as follows:

One change - Rc = 20k Ohms.

I know that for voltage Ub1 in range for +-0.1V (approximately) transistor T2 is in the active mode. And i notice that Uwy1 is constant and this voltage is 5V. So transistor T1 is in cut-off mode. But i don't know how T2 transistor works when Ub1 voltage is less than -0.1V and when Ub1 voltage is greater than 0.1V. Does it work in saturation mode? Could you explain me?

Thanks for the help in advance!