yefj

Advanced Member level 4

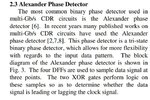

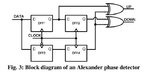

adding reset function to D Flip FLOP for phase detector

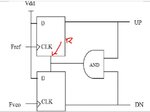

Hello, I have designed a rising edge D-flipflop as shown bellow using CML method.

I could have just connect the output to NMOS switch and discharge it to ground.

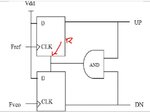

However in our reset signal comes at Q, so basickly if we have Q=1 then this Q=1 is used to turn Q into Q=0.

so we have oscilation.

How do i add "reset" to my D-flip flop So i could use it in phase detector as shown bellow?

Thanks.

Hello, I have designed a rising edge D-flipflop as shown bellow using CML method.

I could have just connect the output to NMOS switch and discharge it to ground.

However in our reset signal comes at Q, so basickly if we have Q=1 then this Q=1 is used to turn Q into Q=0.

so we have oscilation.

How do i add "reset" to my D-flip flop So i could use it in phase detector as shown bellow?

Thanks.

Last edited: