OZZAA

Member level 1

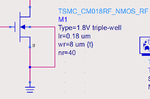

I want to design a power amplifier (PA) while using TSMC 0.18um.

I used the CMOS which has VDD=1.8 volts.

the questions are

can I set the VDD=VDS(Q)= 1.8 V without any proplem?

the instantanous voltage across the trasistor is 2VDD ( VDS(Q)+the amplitude of the signal in case of using RFC inductor.

is it right or i have to make the VDS(Q)= only 0.9V

I used the CMOS which has VDD=1.8 volts.

the questions are

can I set the VDD=VDS(Q)= 1.8 V without any proplem?

the instantanous voltage across the trasistor is 2VDD ( VDS(Q)+the amplitude of the signal in case of using RFC inductor.

is it right or i have to make the VDS(Q)= only 0.9V