TelpDmtr

Newbie level 3

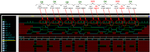

Hello. I have problems in understanding patterns, generated by TetraMax ATPG. I have simple circuits (from ISCAS benchmark) with full-scan DFT. And when I dive into patterns (.wgl or .stil) I see some strange things. 90% is predictable and clear to me:

Now to the problem: in rare cases in the third step scan_select remains "1". It means that we don't capture values from combinational circuit, but loading new value instead of it! Why TetraMAX does it? It makes no sense. Doing this, we just load patterns several times without any feedback from the circuit.

If you have any ideas or suggestions - please let me know. Thank you!

- scan_select is set to "1" (we are in scan shift mode).

- we set up register values in the first clock.

- we set scan_select to "0" (we are looking into combinational circuit outputs), and capture the response in the second clock.

Now to the problem: in rare cases in the third step scan_select remains "1". It means that we don't capture values from combinational circuit, but loading new value instead of it! Why TetraMAX does it? It makes no sense. Doing this, we just load patterns several times without any feedback from the circuit.

If you have any ideas or suggestions - please let me know. Thank you!