Alan8947

Full Member level 4

Hi

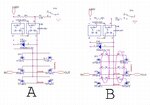

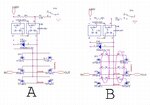

I have one MOSFET failure with S shorted to D and G is 10ohm to S and D. Attached is the schematics, (A) is the original circuit. I use this as SS relay at the output of the hifi power amp, as shown, I use 6 MOSFET to lower the Rdson. The MOSFETs are driven by an opto coupler ASSR-V621 with data sheet:

https://www.digikey.com/product-detail/en/broadcom-limited/ASSR-V621-002E/516-2961-ND/2211292

Let me be specific, I have been using the circuit in a few amps in the pass 4 years, this is the FIRST time one failed. BUT I am paranoid as I designed MOSFET power circuit before and only time I've seen failure like this is oscillation ( local around the MOSFET). MOSFET are usually very rugged. So one failure is alarming to me.

I know it's very common to use a resistor in series with each gate to make the impedance +ve to avoid oscillation, but this circuit is a little different. All the SMPS have low output impedance driver to drive the MOSFET, so gate resistor easily avoid any oscillation. BUT if you look at the datasheet of the ASSR-V621, the drive to the gate of the MOSFET is a photo diode that behave like a current source with very high output impedance, I am not sure it will work even if I put 6 individual resistors on each gate of each MOSFET as shown in circuit (B).

I want to hear opinion on how to better protect the MOSFET from potential oscillation.

Thanks

Alan

- - - Updated - - -

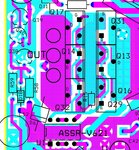

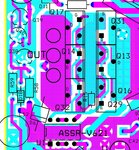

I want to show the layout of the pcb, I did my best to layout with RF in mind as much as possible, I have to use TO-220 as the SMD takes up too much room. You can see I use copper planes as much as possible, there are no long traces running around. Only the gates are connected with traces, all the D and S are connected by copper planes.

I have one MOSFET failure with S shorted to D and G is 10ohm to S and D. Attached is the schematics, (A) is the original circuit. I use this as SS relay at the output of the hifi power amp, as shown, I use 6 MOSFET to lower the Rdson. The MOSFETs are driven by an opto coupler ASSR-V621 with data sheet:

https://www.digikey.com/product-detail/en/broadcom-limited/ASSR-V621-002E/516-2961-ND/2211292

Let me be specific, I have been using the circuit in a few amps in the pass 4 years, this is the FIRST time one failed. BUT I am paranoid as I designed MOSFET power circuit before and only time I've seen failure like this is oscillation ( local around the MOSFET). MOSFET are usually very rugged. So one failure is alarming to me.

I know it's very common to use a resistor in series with each gate to make the impedance +ve to avoid oscillation, but this circuit is a little different. All the SMPS have low output impedance driver to drive the MOSFET, so gate resistor easily avoid any oscillation. BUT if you look at the datasheet of the ASSR-V621, the drive to the gate of the MOSFET is a photo diode that behave like a current source with very high output impedance, I am not sure it will work even if I put 6 individual resistors on each gate of each MOSFET as shown in circuit (B).

I want to hear opinion on how to better protect the MOSFET from potential oscillation.

Thanks

Alan

- - - Updated - - -

I want to show the layout of the pcb, I did my best to layout with RF in mind as much as possible, I have to use TO-220 as the SMD takes up too much room. You can see I use copper planes as much as possible, there are no long traces running around. Only the gates are connected with traces, all the D and S are connected by copper planes.