komax

Junior Member level 3

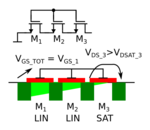

Let's say I have 5 NMOS with size W/L connected in series (stacked) with gate connected together, from what I understand this is functionally equivalent to a single NMOS with size W/5L.

In terms of saturation check only the top NMOS will be in saturation while the other 4 will be in triode. My question is regarding this saturation check, specifically when checking Vgs - Vth > 100mV for achieving strong inversion. The Vgs in that equation, is this the Vgs of the top NMOS or the bottom?

I'm thinking that it's the bottom NMOS, my logic is as follow: Suppose the gate voltage is Vb (wrt ground), if I have a single transistor with size W/5L my Vgs will simply be Vb, and since my stacked transistor is supposed to be equivalent if I take the Vgs of the top transistor my Vgs will no longer be Vb. If I take the Vgs of the top NMOS it is much harder to maintain strong inversion, this is especially so the more I stack the NMOS because the Vgs will simply be Vb - Vx (v at source) and Vx is getting higher and higher as I stack more. This isn't the case if I use single transistor with W/5L, W/10L, W/20L, my Vgs stays Vb (to ground).

Please help me understand.

Thank you in advance for your help.

In terms of saturation check only the top NMOS will be in saturation while the other 4 will be in triode. My question is regarding this saturation check, specifically when checking Vgs - Vth > 100mV for achieving strong inversion. The Vgs in that equation, is this the Vgs of the top NMOS or the bottom?

I'm thinking that it's the bottom NMOS, my logic is as follow: Suppose the gate voltage is Vb (wrt ground), if I have a single transistor with size W/5L my Vgs will simply be Vb, and since my stacked transistor is supposed to be equivalent if I take the Vgs of the top transistor my Vgs will no longer be Vb. If I take the Vgs of the top NMOS it is much harder to maintain strong inversion, this is especially so the more I stack the NMOS because the Vgs will simply be Vb - Vx (v at source) and Vx is getting higher and higher as I stack more. This isn't the case if I use single transistor with W/5L, W/10L, W/20L, my Vgs stays Vb (to ground).

Please help me understand.

Thank you in advance for your help.