hamidkavianathar

Member level 5

hey guys

I have designed a custom board with a fpga. when I do initialize chain in iMPACT I recevice this message:

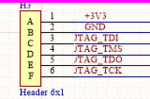

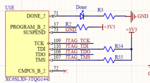

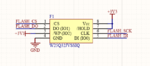

here is my schematic:

could you please tell what is wrong with my board?

thanks in advance.

I have designed a custom board with a fpga. when I do initialize chain in iMPACT I recevice this message:

I have measured the voltage of all vcc pins. they are correct. but some IO pins have strange values. for example the voltage of them is 1.5 v.Attempting to identify devices in the boundary-scan chain configuration...

INFO:iMPACT - Current time: 9/28/2019 5:34:02 PM

PROGRESS_START - Starting Operation.

Identifying chain contents...INFO:iMPACT:1588 - '0':The part does not appear to be Xilinx Part.

'0': : Manufacturer's ID =Unknown , Version : 15

INFO:iMPACT:501 - '1': Added Device UNKNOWN successfully.

----------------------------------------------------------------------

----------------------------------------------------------------------

done.

PROGRESS_END - End Operation.

Elapsed time = 0 sec.

here is my schematic:

could you please tell what is wrong with my board?

thanks in advance.