mifio

Newbie

Dear all,

I'm facing a problem with a post-pnr simulation that I hope you can help me figure out.

The design flow is based on the GPDK045 kit from Cadence. I use Genus & Innovus for synthesis & pnr, Modelsim for simulations, and I have compiled the standard cell library with modelsim for gate-level simulations.

Post-synthesis, my timing constraints are met and the simulation of the netlist+SDF works as expected. Post-pnr, my timing constraints are also met, however the simulation reports setup violations on many flops, which leads to erroneous results.

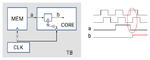

The design is a very simple processor core with only 1 clock. The target timing constraints is 1000 ps. Of course the test bench produces a matching clock of 1000 ps, but I even noticed that the problem remains with 1200 ps and 1500 ps.

The main reason why I need these gate level simulations is to generate the SAIF file for more accurate power evaluation. Also, my design being small the simulations (when working) are quite fast.

What I have tried/think-of so far:

I'm running out of idea, so I need your wisdom. Thank you very much for your time.

I'm facing a problem with a post-pnr simulation that I hope you can help me figure out.

The design flow is based on the GPDK045 kit from Cadence. I use Genus & Innovus for synthesis & pnr, Modelsim for simulations, and I have compiled the standard cell library with modelsim for gate-level simulations.

Post-synthesis, my timing constraints are met and the simulation of the netlist+SDF works as expected. Post-pnr, my timing constraints are also met, however the simulation reports setup violations on many flops, which leads to erroneous results.

The design is a very simple processor core with only 1 clock. The target timing constraints is 1000 ps. Of course the test bench produces a matching clock of 1000 ps, but I even noticed that the problem remains with 1200 ps and 1500 ps.

The main reason why I need these gate level simulations is to generate the SAIF file for more accurate power evaluation. Also, my design being small the simulations (when working) are quite fast.

What I have tried/think-of so far:

- I have used many sdf options in Innovus to generate the SDF, but basically I use -version 2.1 to match the standard cells, and -target_application verilog to optimize the sdf for simulations

- I tried to do formal equivalence with the post-synthesis netlist but the version of the lec tool available has a bug.

- Maybe a mismatch between the operating conditions used in the backend vs simulation ? Here I use the fast timing library (.lib) and qrc, and I compiled the fast version of the stdcell with modelsim.

- Maybe a problem with the kit ? Anyone having a similar issue ?

I'm running out of idea, so I need your wisdom. Thank you very much for your time.