padfoot_1729

Newbie level 1

Hi guys,

I had been practicing a few problems in verilog and got stuck on this :

Question : write a program so that output should be 1 when 'x' is greater than or equal to 'y'

x and y are binary

My logic module:

My stimulus/ test-bench module :

--------------------------------------------

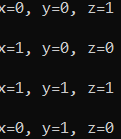

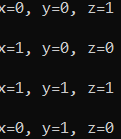

OUTPUT OBTAINED:

Please Help with the above issue, output is shown as 0 when x=1 and y=0.

Thank you!!

I had been practicing a few problems in verilog and got stuck on this :

Question : write a program so that output should be 1 when 'x' is greater than or equal to 'y'

x and y are binary

My logic module:

Code Verilog - [expand]

My stimulus/ test-bench module :

Code Verilog - [expand]

--------------------------------------------

OUTPUT OBTAINED:

Please Help with the above issue, output is shown as 0 when x=1 and y=0.

Thank you!!

Last edited by a moderator: