andrew_que

Junior Member level 2

Hello everyone.

I recently bought a bunch of Altera MAX 7000A CPLDs on RS components in the plcc44 package.

I already have at home one of those cheap clones altera usb blaster with JTAG output.

I tried a simple breadboard setup to program the cpld with altera quartus without success.

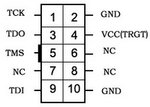

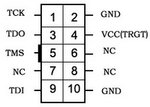

First, the only useful information about programming in the CPLD datasheet is that it complies to the "industry-standard 4-pin IEEE Std. 1149.1" interface, which would be TDI,TDO,TMS,TCK. Now I found all those pins on my CPLD pinout. I'm providing 3.3V to one VCC pin of the CPLD and using common ground for my PSU, CPLD and USB Blaster JTAG. I've also found the pinout of the JTAG connector from the USB blaster. There are 10 pins but 3 of them are NC and one is a doubled GND. The first attached figure shows how I wired it all (I found the pullup/down res configuration from the schematic of the chinese FPGA devboard where my usb blaster came from). Quartus doesen't recognize my cpld. I'm sure my quartus (ver II 13.0) has support to the device because I got to choose it during the new project wizard. Actually, in the software I selected EPM7032AELC44-10 whereas mine has an additional N at the end, though I don't think this can make a difference.

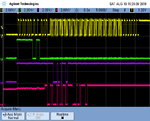

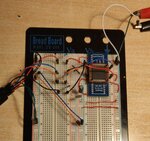

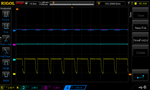

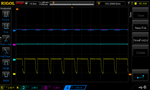

I have tried changing USB port (3.0 and a 1.0 in the front panel, and a 3.0 in the back panel directly connected to the mobo). I have tried changing the USB cable. So I went ahead and hooked up my DSO to the four JTAG pins and got some waveforms obtained while trying to get quartus recognize my cpld (Auto Detect button, second attached figure). The third figure gives an overall of the process. Now, I'm not an expert of jtag but it looks quite strange that TCLK would not tick while data is sent throught TDI. Also, fourth figure shows a detail of TCK in the final portion of the waveform and to me it looks a bit odd that they would go with 90%ish duty cycle... Is it possible that my usb blaster is fried? I used it so little and always kept it inside its box, never exposing to heat/water, also I opened it and it looks fine. Maybe I'm using the wrong pin, I'm using a picture found online as reference (fifth attached figure)

Do you have any suggestions? I really thought this would have been easier... but now I'm engaged to try and solve this.

attached figures

Schematic:

Quartus recognizes USB BLASTER but fails to recognize CPLD:

JTAG Scan process measurements:

TCK detail after the TDI run:

USB BLASTER pinout reference:

I recently bought a bunch of Altera MAX 7000A CPLDs on RS components in the plcc44 package.

I already have at home one of those cheap clones altera usb blaster with JTAG output.

I tried a simple breadboard setup to program the cpld with altera quartus without success.

First, the only useful information about programming in the CPLD datasheet is that it complies to the "industry-standard 4-pin IEEE Std. 1149.1" interface, which would be TDI,TDO,TMS,TCK. Now I found all those pins on my CPLD pinout. I'm providing 3.3V to one VCC pin of the CPLD and using common ground for my PSU, CPLD and USB Blaster JTAG. I've also found the pinout of the JTAG connector from the USB blaster. There are 10 pins but 3 of them are NC and one is a doubled GND. The first attached figure shows how I wired it all (I found the pullup/down res configuration from the schematic of the chinese FPGA devboard where my usb blaster came from). Quartus doesen't recognize my cpld. I'm sure my quartus (ver II 13.0) has support to the device because I got to choose it during the new project wizard. Actually, in the software I selected EPM7032AELC44-10 whereas mine has an additional N at the end, though I don't think this can make a difference.

I have tried changing USB port (3.0 and a 1.0 in the front panel, and a 3.0 in the back panel directly connected to the mobo). I have tried changing the USB cable. So I went ahead and hooked up my DSO to the four JTAG pins and got some waveforms obtained while trying to get quartus recognize my cpld (Auto Detect button, second attached figure). The third figure gives an overall of the process. Now, I'm not an expert of jtag but it looks quite strange that TCLK would not tick while data is sent throught TDI. Also, fourth figure shows a detail of TCK in the final portion of the waveform and to me it looks a bit odd that they would go with 90%ish duty cycle... Is it possible that my usb blaster is fried? I used it so little and always kept it inside its box, never exposing to heat/water, also I opened it and it looks fine. Maybe I'm using the wrong pin, I'm using a picture found online as reference (fifth attached figure)

Do you have any suggestions? I really thought this would have been easier... but now I'm engaged to try and solve this.

attached figures

Schematic:

Quartus recognizes USB BLASTER but fails to recognize CPLD:

JTAG Scan process measurements:

TCK detail after the TDI run:

USB BLASTER pinout reference: