crutschow

Advanced Member level 6

- Joined

- Feb 22, 2012

- Messages

- 4,454

- Helped

- 998

- Reputation

- 1,994

- Reaction score

- 1,121

- Trophy points

- 1,393

- Location

- Colorado USA Zulu -7

- Activity points

- 25,244

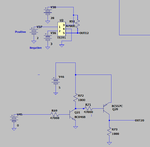

That's only one input condition out of four possible.I need an OR logic, if one input is 1 then the output of the wired is 1 and the PMOSFET is turn off.

What about both inputs zero?

What about both inputs one?