mrinalmani

Advanced Member level 1

- Joined

- Oct 7, 2011

- Messages

- 463

- Helped

- 60

- Reputation

- 121

- Reaction score

- 58

- Trophy points

- 1,318

- Location

- Delhi, India

- Activity points

- 5,285

Hi

I am testing an H-Bridge circuit and it is heating up without load.

The MOSFET is IPD60R180C7 (600V, 180mOhm Infineon MOSFET). Supply voltage is 250VDC and switching frequency is 100KHz. There's 10nF MLCC immediately close to the bridge and another 100uF electrolytes further away. Trace width between gate and driver is approximately 60mm but nearly differential.

There is sufficient dead band of over 250ns and I am quite sure there is no overlap. Coss is rather small at 40pF and should play no major role in heating. Loss calculation by thermal techniques depict over 10W loss.

The issue here is Miller spike on the gates of the MOSFETs when the other MOSFET makes a transition. When the upper FET turns on, there is spike on the gate of the lower FET and vice versa. I have seen similar conditions earlier but the spikes in general are limited to less than a volt or two. But this time with this circuit the spikes are severe and measure over 5V. I understand that the probes must be exaggerating the spike but nevertheless it is very much present and 10W of loss confirms there's something wrong.

I have tried different values of gate resistor from 1 Ohm to 15 Ohm but it doesn't help. I have also used slow turn-on (15 ohm) and fast turn off (2 Ohm in series with diode) but again it doesn't help.

Any one with some sort of experience with this situation please share your views. Any help would be deeply appreciated.

I am posting images below:

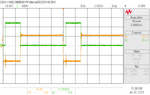

(Lower MOSFET Vds-orange, Vgs-green)

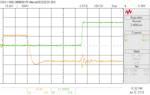

(Upper MOSFET Vds-green, Vgs-orange)

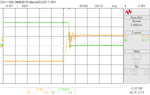

(Vds rise and fall time)

(Vds negative transient during falling edge)

Thank you!

I am testing an H-Bridge circuit and it is heating up without load.

The MOSFET is IPD60R180C7 (600V, 180mOhm Infineon MOSFET). Supply voltage is 250VDC and switching frequency is 100KHz. There's 10nF MLCC immediately close to the bridge and another 100uF electrolytes further away. Trace width between gate and driver is approximately 60mm but nearly differential.

There is sufficient dead band of over 250ns and I am quite sure there is no overlap. Coss is rather small at 40pF and should play no major role in heating. Loss calculation by thermal techniques depict over 10W loss.

The issue here is Miller spike on the gates of the MOSFETs when the other MOSFET makes a transition. When the upper FET turns on, there is spike on the gate of the lower FET and vice versa. I have seen similar conditions earlier but the spikes in general are limited to less than a volt or two. But this time with this circuit the spikes are severe and measure over 5V. I understand that the probes must be exaggerating the spike but nevertheless it is very much present and 10W of loss confirms there's something wrong.

I have tried different values of gate resistor from 1 Ohm to 15 Ohm but it doesn't help. I have also used slow turn-on (15 ohm) and fast turn off (2 Ohm in series with diode) but again it doesn't help.

Any one with some sort of experience with this situation please share your views. Any help would be deeply appreciated.

I am posting images below:

(Lower MOSFET Vds-orange, Vgs-green)

(Upper MOSFET Vds-green, Vgs-orange)

(Vds rise and fall time)

(Vds negative transient during falling edge)

Thank you!