sandeep_sggs

Full Member level 2

Hello,

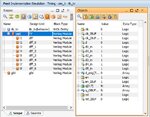

I am trying to perform post implementation timing simulation of attached circuit in vivado 2016.2(). I am able to do behavioral simulation with all the objects visible (pls refer attached eda_bs). But when i start post implementation timing simulation, i am unable to see d[0:7] listed in objects tab(pls refer attached eda_pits).

Anyone can guess the reason?

code:

Testbench

I am trying to perform post implementation timing simulation of attached circuit in vivado 2016.2(). I am able to do behavioral simulation with all the objects visible (pls refer attached eda_bs). But when i start post implementation timing simulation, i am unable to see d[0:7] listed in objects tab(pls refer attached eda_pits).

Anyone can guess the reason?

code:

Code VHDL - [expand]

Testbench

Code VHDL - [expand]

Attachments

Last edited by a moderator: