Danie.

Newbie level 5

Hello,

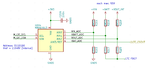

i am about to design a buck boost Battery Charger with the LTC4020.

Design requirements:

- 10A charge current

- charge current adjustable

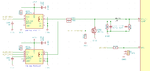

- 10V ... 48V input voltage

- different types of batterys (1s ... 12s LiPo, 6V, 12V, 24V lead accid -> adjustable output voltage range: 3V ... 53V)

- fully adjustable from a microcontroller

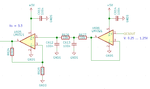

The first problem i have is to calculate the min. inductor value.

The datasheet is not really clear here and i am a bit confused about the use of IMAX and ILMAX and which one to use in the equations.

From the datasheet:

Following this description, the worst cases are:

Buck: VinMax -> Vout = Vin/2 (48V -> 24V)

Lmin = (24V*(24V/48V)) / (120kHz*5A*10*) -> 2µH

Boost: VinMax -> VoutMax (48V -> 53V)

Lmin = (48V*(1-(48V/53V)) / (120kHz*11,45A*10A)) -> ~ 1,06µH

For me these values seems to be quite a lot to small!? Did i miss something here?

The Eval Board uses a 5,6µH Inductor.

For me this seems to be completely wrong? :-o

Is this requirement possible at all?

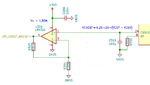

If yes, how to adjust the voltage from an microcontroller?

Maybe a current sink DAC, wich adjusts the feedback node could do the job?

Current adjustment is done by sinking 0 to 50uA out from the RNG/SS and ILIM pin. So this should be quite easy.

Kind Regards

Danie

i am about to design a buck boost Battery Charger with the LTC4020.

Design requirements:

- 10A charge current

- charge current adjustable

- 10V ... 48V input voltage

- different types of batterys (1s ... 12s LiPo, 6V, 12V, 24V lead accid -> adjustable output voltage range: 3V ... 53V)

- fully adjustable from a microcontroller

The first problem i have is to calculate the min. inductor value.

The datasheet is not really clear here and i am a bit confused about the use of IMAX and ILMAX and which one to use in the equations.

From the datasheet:

For step-down conversion, use the maximum expected operating voltage for VIN(MAX). If the expected VOUT

operating range (typically from VFBMIN = 2.125V to VFBMAX = 2.75V) includes VIN(MAX)/2, use that value for VOUT.

If the entire operating range is below VIN(MAX)/2, use the value corresponding to VFBMAX = 2.75V. If the entire operating

range is above VIN(MAX)/2, use the value correspondingto VFBMIN = 2.125V.

For step-up conversion, use the maximum output voltage (typically corresponding to pin VFBMAX = 2.75V) for VOUT(MAX).

If the expected VIN operating range includes VOUT(MAX)/2, use that value for VIN.

If the entire input operating range is below VOUT(MAX)/2, use the maximum operating voltage for VIN. If the entire input

operating range is above VOUT(MAX)/2, use the minimum input operating voltage for VIN.

Following this description, the worst cases are:

Buck: VinMax -> Vout = Vin/2 (48V -> 24V)

Lmin = (24V*(24V/48V)) / (120kHz*5A*10*) -> 2µH

Boost: VinMax -> VoutMax (48V -> 53V)

Lmin = (48V*(1-(48V/53V)) / (120kHz*11,45A*10A)) -> ~ 1,06µH

For me these values seems to be quite a lot to small!? Did i miss something here?

The Eval Board uses a 5,6µH Inductor.

So i would use a 5,6µH inductor with an RMS current of >= 10A and a saturation of 10A*1,25 = 12,5A?Magnetics vendors typically specify inductors with maximum RMS and saturation current ratings.

Select an inductor that has a saturation current rating at or above 1.25 • IMAX, and an RMS rating above IMAX.

For me this seems to be completely wrong? :-o

Is this requirement possible at all?

If yes, how to adjust the voltage from an microcontroller?

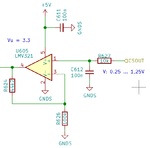

Maybe a current sink DAC, wich adjusts the feedback node could do the job?

Current adjustment is done by sinking 0 to 50uA out from the RNG/SS and ILIM pin. So this should be quite easy.

Kind Regards

Danie