KingDarius6288

Junior Member level 2

Hi all;

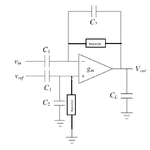

I have designed a two-stage OTA with Miller compensation. The first stage is Folded Cascode and the second one is a simple common source. The DC gain is 88dB and PM=35 deg. The load is a 10pF capacitor. I want to test it with capacitive feedback as below (attachment). The value of the resistor is very high and the C1 and C2 are in pF range. I have two questions:

1- Should the DC levels of Vin and Vout be equal? since the capacitive coupling f the input indicates that DC level of the input is zero, and the output DC level is not, I am somehow confused.

2- when I close the loop, voltage gain drops to negative dB values. can anyone suggest the reason and the solution?

Thank you in advance.

I have designed a two-stage OTA with Miller compensation. The first stage is Folded Cascode and the second one is a simple common source. The DC gain is 88dB and PM=35 deg. The load is a 10pF capacitor. I want to test it with capacitive feedback as below (attachment). The value of the resistor is very high and the C1 and C2 are in pF range. I have two questions:

1- Should the DC levels of Vin and Vout be equal? since the capacitive coupling f the input indicates that DC level of the input is zero, and the output DC level is not, I am somehow confused.

2- when I close the loop, voltage gain drops to negative dB values. can anyone suggest the reason and the solution?

Thank you in advance.