venn_ng

Member level 5

I have attached a figure that shows buffer in both non-inverting (a) and inverting configuration (b). Out of these two, which one is better if the op-amp has an offset.

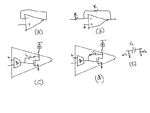

In (c), (d), I am trying to do miller compensation with pole-zero cancellation. Which one of (c), (d) is better (especially when Cc has parastic caps that's proportional to Cc as shown in (e))?

In (c), (d), I am trying to do miller compensation with pole-zero cancellation. Which one of (c), (d) is better (especially when Cc has parastic caps that's proportional to Cc as shown in (e))?