Vishal_thomas

Newbie level 4

Hai,

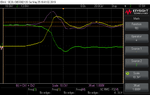

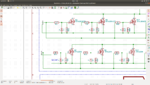

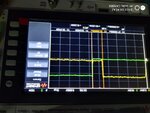

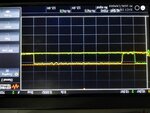

I am using IXFX180N25T mosfet for motor controller. Driving 8 mosfets in parallel in each leg with Infenion gate driver followed by current booster using transistor totem pole configuration. I used a series gate resistor of 1ohm for each individual mosfet after current Booster circuit. Each mosfet has 10K pull down and ceramic cap of 10nf at Gate-source.V/f algorithm with base rpm set to 3000 and max bus voltage 72V. Every time one mosfet of high side leg is getting burned, i have provided dead band of 5microsec.

The circuit is mounted on heat sink.I can see some unwanted triggering happening in mosfet because phase output is very high than expected.

The whole circuits works fine when am using infenion AUIRFP4568.

Kindly let me know any suggestions.

I am using IXFX180N25T mosfet for motor controller. Driving 8 mosfets in parallel in each leg with Infenion gate driver followed by current booster using transistor totem pole configuration. I used a series gate resistor of 1ohm for each individual mosfet after current Booster circuit. Each mosfet has 10K pull down and ceramic cap of 10nf at Gate-source.V/f algorithm with base rpm set to 3000 and max bus voltage 72V. Every time one mosfet of high side leg is getting burned, i have provided dead band of 5microsec.

The circuit is mounted on heat sink.I can see some unwanted triggering happening in mosfet because phase output is very high than expected.

The whole circuits works fine when am using infenion AUIRFP4568.

Kindly let me know any suggestions.