Junus2012

Advanced Member level 5

Dear friends,

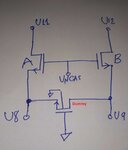

attached you see please my matched array for the given circuit.

As you can see that in the first array management every transistor was individual and the distance are identical between every gate.

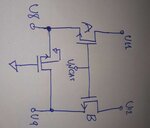

In the second arrangement I merged the shared region to reduce the size of the layout, but as you see that distance are not becoming identical between each transistor in the array.

I don't know if that will effect the matching or not, but I have a feeling that the electrical characteristics of both might be different,

which one should be better ?

Thank you very much

attached you see please my matched array for the given circuit.

As you can see that in the first array management every transistor was individual and the distance are identical between every gate.

In the second arrangement I merged the shared region to reduce the size of the layout, but as you see that distance are not becoming identical between each transistor in the array.

I don't know if that will effect the matching or not, but I have a feeling that the electrical characteristics of both might be different,

which one should be better ?

Thank you very much