daniel442

Junior Member level 2

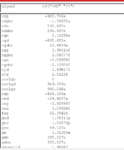

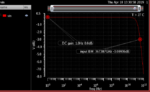

I would like to compare my pole simulation results to my hand calculations, I'm receiving quite a big error. when simulating a Common Source stage without output capacitance load there is a big difference between the simulated and the calculated poles, when I'm adding a capacitor load the output pole is similar but the input (which didn't change) is not... maybe I didn't model the MOSFET correctly?