Junus2012

Advanced Member level 5

Dear all,

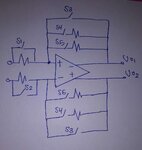

I am trying to design a CMOS TG with Ron = 10 Ohm maximum because I want to use it as an switch. But it is becoming difficult to reach this value and I need to increase the size of the MOS too much which leads to increase the parasitic capacitors and the switching time.

Do you think the 10 Ohm is not realistic or practical value for CMOS TG ? or these is other technique to reduce it further

Thank you

I am trying to design a CMOS TG with Ron = 10 Ohm maximum because I want to use it as an switch. But it is becoming difficult to reach this value and I need to increase the size of the MOS too much which leads to increase the parasitic capacitors and the switching time.

Do you think the 10 Ohm is not realistic or practical value for CMOS TG ? or these is other technique to reduce it further

Thank you