Junus2012

Advanced Member level 5

Dear Friends,

I am tried different kind of standard compensation typologies to compensate my CMFB, but non of them worked with me,

Today and Just by trying, I connected one capacitors from the midpoint of the average common mode resistors to the ground and the circuit is compensated very well,

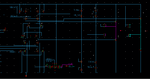

Kindly I have attached you the picture of my CMFB amplifier showing the connection of this capacitor,

I didn't find some people compensating in such away, therefore I don't know if it possible to consider it in my work or might be there is other side effect which I don't know, therefore I would like to ask your opinion about it.

Generally as I increase the compensation capacitor the CMFB becomes more stable, because the GBW of the CMFB becomes less and less. This concept is basically should work if I connect it to the output as usual as for any amplifier, again if I would move it to the output it will not work

Thank you in advance

I am tried different kind of standard compensation typologies to compensate my CMFB, but non of them worked with me,

Today and Just by trying, I connected one capacitors from the midpoint of the average common mode resistors to the ground and the circuit is compensated very well,

Kindly I have attached you the picture of my CMFB amplifier showing the connection of this capacitor,

I didn't find some people compensating in such away, therefore I don't know if it possible to consider it in my work or might be there is other side effect which I don't know, therefore I would like to ask your opinion about it.

Generally as I increase the compensation capacitor the CMFB becomes more stable, because the GBW of the CMFB becomes less and less. This concept is basically should work if I connect it to the output as usual as for any amplifier, again if I would move it to the output it will not work

Thank you in advance