tenso

Advanced Member level 4

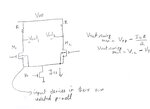

I have some questions regarding output voltage swing, it's relationship to the input common voltage and the threshold voltage. In the attached figure the output voltage can swing between Vout,max_swing = VDD - ISS/2 * RD (where ISS/2 is the current when the input differential voltage is zero) and Vout,min_swing= VIC - VTH.

So it follows that having a high VIC is detrimental to swing in both directions because increasing VIC increases the current and the voltage drop across RD, decreasing Vout,max_swing. A high VIC increases Vout,min_swing as well.

Now if we had diff. pair where the NMOS transistors had their own isolated pwells so that the source and bulk can be tied together. This prevents the VTH from increasing and the required bias VIC from increasing.

So is my reasoning right, here?

If we have an input diff pair in isolated wells, besides helping with PSRR or substrate noise, it also helps with output swing(?).

if we can afford the space, does tying the source and bulk of input diff pair increase the output swing?