inass57

Member level 2

Hi guys!

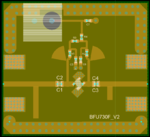

I've been trying to design an LNA using BJT transistor, on the first try the results of my simulations and measurements were different and i concluded that it must have been related to the permittivity of the substrate (i had a resonator on the board) . so i redesigned the LNA using the correct permittivity this time but still no luck.

So i was wondering how accurate the transistor model is actually? and if they are not 100% accurate how does a person design correctly their amplifier?

I'm working at 10GHz.

Thank you in advance.

I've been trying to design an LNA using BJT transistor, on the first try the results of my simulations and measurements were different and i concluded that it must have been related to the permittivity of the substrate (i had a resonator on the board) . so i redesigned the LNA using the correct permittivity this time but still no luck.

So i was wondering how accurate the transistor model is actually? and if they are not 100% accurate how does a person design correctly their amplifier?

I'm working at 10GHz.

Thank you in advance.

Last edited: