shragh

Newbie level 3

Hi,

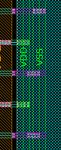

I am working on digital ASIC backend design using IC Compiler. I have power rings created around all the macros in my design. After P&R, there are shorts between VDD and VSS nets reported by LVS check in both ICC and Calibre. The problem happens due to bad alignment of some of the vias connecting the macro ground nets to the ring (image attached), that overlap with the power net, thereby causing the short.

There are too many of these incorrectly aligned vias in the design to manually move each of them. If anyone has faced a similar issue, is there a way to avoid (or rectify) this? Also, how can I investigate the cause for this? I don't think it can be a blockage in the macro since this doesn't happen for all the vias on a particular side of the macro, only some of them. For instance, in the image attached, the vias on the top (and everything above it in the actual design) are correctly aligned, but everything below is incorrectly aligned.

I'd appreciate any inputs on this.

Thanks,

Shashank

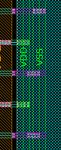

I am working on digital ASIC backend design using IC Compiler. I have power rings created around all the macros in my design. After P&R, there are shorts between VDD and VSS nets reported by LVS check in both ICC and Calibre. The problem happens due to bad alignment of some of the vias connecting the macro ground nets to the ring (image attached), that overlap with the power net, thereby causing the short.

There are too many of these incorrectly aligned vias in the design to manually move each of them. If anyone has faced a similar issue, is there a way to avoid (or rectify) this? Also, how can I investigate the cause for this? I don't think it can be a blockage in the macro since this doesn't happen for all the vias on a particular side of the macro, only some of them. For instance, in the image attached, the vias on the top (and everything above it in the actual design) are correctly aligned, but everything below is incorrectly aligned.

I'd appreciate any inputs on this.

Thanks,

Shashank