d123

Advanced Member level 5

Hi,

Working on a theoretical circuit and I was wondering if there are any viable and reliable alternatives to using a Zener diode to protect the MOSFET gate from over voltages.

It crossed my mind that an op amp clamp may be feasible but perhaps not up to the job/powerful enough.

No problems with PCB size or suchlike, willing to give anything discrete-based and suitable a go, just seeking input about alternatives to Zener diodes.

Any suggestions?

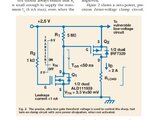

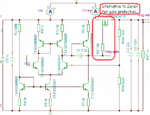

Example schematic to show what is being referred to:

Thanks.

Working on a theoretical circuit and I was wondering if there are any viable and reliable alternatives to using a Zener diode to protect the MOSFET gate from over voltages.

It crossed my mind that an op amp clamp may be feasible but perhaps not up to the job/powerful enough.

No problems with PCB size or suchlike, willing to give anything discrete-based and suitable a go, just seeking input about alternatives to Zener diodes.

Any suggestions?

Example schematic to show what is being referred to:

Thanks.