bravoegg

Member level 2

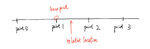

So if there are four integer point : point0 point1 point2 and point3

Set downsampling point at the fractional point location 0.1. The value of point 0.1 could be calculated using Lagrange interpolation.

In matlab it’s very easy to calculate the downsampling location point: mod(downsampling_factor*(0:n), 1). The downsampling_factor is between [1,2).

My problem is that there’re arbitrary downsampling rates, so it’s impossible to store the downsampling location in lookup table...that’ll be only valid for one downsampling rate.

Suppose the incoming data sampling rate fs, output downsampled rate fd, and downsampling_factor are known, I want to know how do I calculate the exact downsampling point location in FPGA?

I don’t need to know the absolute time location, just the relative location between like point1 and point2, that is The interval between point 1 and point2 is divided into smaller sections, if point1 is used as base point in Lagrange.

To add a few things, the system clock is fs(also the incoming data rate). And the output downsampled rate fd is generated using dds(because the downsamping factor is known), also using system clock fs. So fs and fd are synchronous.

Set downsampling point at the fractional point location 0.1. The value of point 0.1 could be calculated using Lagrange interpolation.

In matlab it’s very easy to calculate the downsampling location point: mod(downsampling_factor*(0:n), 1). The downsampling_factor is between [1,2).

My problem is that there’re arbitrary downsampling rates, so it’s impossible to store the downsampling location in lookup table...that’ll be only valid for one downsampling rate.

Suppose the incoming data sampling rate fs, output downsampled rate fd, and downsampling_factor are known, I want to know how do I calculate the exact downsampling point location in FPGA?

I don’t need to know the absolute time location, just the relative location between like point1 and point2, that is The interval between point 1 and point2 is divided into smaller sections, if point1 is used as base point in Lagrange.

To add a few things, the system clock is fs(also the incoming data rate). And the output downsampled rate fd is generated using dds(because the downsamping factor is known), also using system clock fs. So fs and fd are synchronous.

Last edited: