smita1811

Newbie level 6

Hello All,

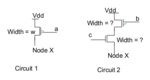

In some part of my circuit, there is a pmos transistor connected between Vdd and node X (circuit 1) and width=w as shown in the image linked below (querypmos.png) . In another circuit, a series of pmos and nmos transitors are connected between Vdd and node X (circuit 2). What will be the widths of pmos and nmos transitors so that the effective width is w between node Vdd and X?

As per the theory of logical effort in cmos circuit, the widths for two nmos(pmos) series transistors is 2w each in order to get the effective width of w. But in this case the transistors are the same i.e. either nmos or pmos. Can we apply this theory to the different transistors i.e one pmos and one nmos in series?

Thanks

In some part of my circuit, there is a pmos transistor connected between Vdd and node X (circuit 1) and width=w as shown in the image linked below (querypmos.png) . In another circuit, a series of pmos and nmos transitors are connected between Vdd and node X (circuit 2). What will be the widths of pmos and nmos transitors so that the effective width is w between node Vdd and X?

As per the theory of logical effort in cmos circuit, the widths for two nmos(pmos) series transistors is 2w each in order to get the effective width of w. But in this case the transistors are the same i.e. either nmos or pmos. Can we apply this theory to the different transistors i.e one pmos and one nmos in series?

Thanks